# Karnaugh Minimizer

Using Karnaugh Minimizer Pro

Congratulations on choosing Karnaugh Minimizer Professional - the world's #1 boolean minimization software.

This advanced minimization tool quickly generate a high-quality solution. You can convert boolean function to **VHDL** or **Verilog** code or create schematic with NAND gates. Also, Karnaugh Minimizer has a report generation tool that you can use to create reports of minimization process

This guide contains links to third-party Web sites that are not under the control of ShurikSoft, and ShurikSoft is not responsible for the content on any linked site. If you access a third-party Web site mentioned in this guide, then you do so at your own risk. ShurikSoft provides these links only as a convenience, and the inclusion of the link does not imply that ShurikSoft endorses or accepts any responsibility for the content on those third-party sites.

Copyright © 2002 - 2004 ShurikSoft, All rights reserved. This manual may not be copied, photocopied, reproduced, translated, or converted to any electronic or machine-readable form in whole or in part without prior written approval of ShurikSoft,

First Edition: February 2004

ShurikSoft. Yazikova St. Donetsk, Ukraine 83101

# **CONTENTS**

| HAPTER 1: Introduction               |    |

|--------------------------------------|----|

| About Karnaugh Minimizer Pro         | 4  |

| What's new in Karnaugh Minimizer Pro | 5  |

| Sources of information               |    |

| HAPTER 2: User Interface description |    |

| Using project tree                   | 7  |

| Using tabbed panel                   | 9  |

| HAPTER 3: Tabs description           | 10 |

| Function tab                         | 10 |

| Karnaugh Map tab                     | 11 |

| Quine Mc Cluskey tab                 | 12 |

| Circuit tab                          | 13 |

| Report tab                           | 14 |

| VHDL tab                             |    |

| Verilog tab                          | 16 |

| Converter tab                        |    |

| HAPTER 4: Theory                     | 18 |

| SOP and POS notation                 |    |

| Decimal notation                     |    |

### **About Karnaugh Minimizer Professional**

Boolean Algebra assistant program is an interactive program extremely easy to use. A must-have tool for the freshmen electrical engineering student.

The program is intended for the developers of small digital devices and radioamateurs, also for those who is familiar with Boolean algebra, mostly for electrical engineering students.

Karnaugh Minimizer program is called to facilitate minimization of Boolean function by a method of Karnaugh maps. The program has the simple and convenient interface, evident image of received results of minimization. The program draws the so-called largest circle and displays the prime implicant solution.

With Karnaugh Minimizer, a proven boolean minimization tool, you can effeciently design small circuits and logical schemas, Karnaugh Minimizer handles the widest variety of boolean function representations, letting you to choose convenient way of presenting your boolean functions.

With Karnaugh Minimizer Professional, you can now do all of the following:

- Receive output in either SOP(DNF) or POS(CNF) format

- · Find and eliminate redundant terms

- · Handle don't care conditions

- Formula to schematic tool convert boolean formula to NAND or AND/OR schematic. supported European and USA gate systems

- Use Quine Mc Cluskey method minimization tool to handle 4-23 variables

- Convert boolean formula to VHDL or Verilog code

- Allows you to click on a term in a given expression and view it on the map.

The program will indicate the corresponding term with a fill cells

- Draw 2 8 variable Karnaugh Map

- Simplifies expressions that you type in

- Fill map with several ways Truth table, Sets, Boolean formula

- Export Map to HTML table to easyer creation of synthesis reports

- · Automated creation of reports after analyze

# What's new in Karnaugh Minimizer Professional version

- Absolutely new user interface + WinXP themes support

- Size of installation package was reduced in about two times

- More user friendly than ever

- Increased enhancement potential

- Converter tool allow you to convert Boolean function between different representations of it (K-map, Sets, Truth table)

#### **Sources of information**

Useful links to information about Karnaugh minimization method:

- Theory of Karnaugh Maps http://www.ee.surrey.ac.uk/Projects/Labview/minimisation/karnaugh.html

- Book about Boolean algebra and Karnaugh Minimization http://www.maxmon.com/kmaps1.htm

- Minimization of Boolean expressions using Karnaugh maps http://www.cs.usm.maine.edu/~welty/karnaugh.htm

- Logic Minimization

http://www.cs.byu.edu/courses/cs143/reading/karnaugh.html

## Using project tree

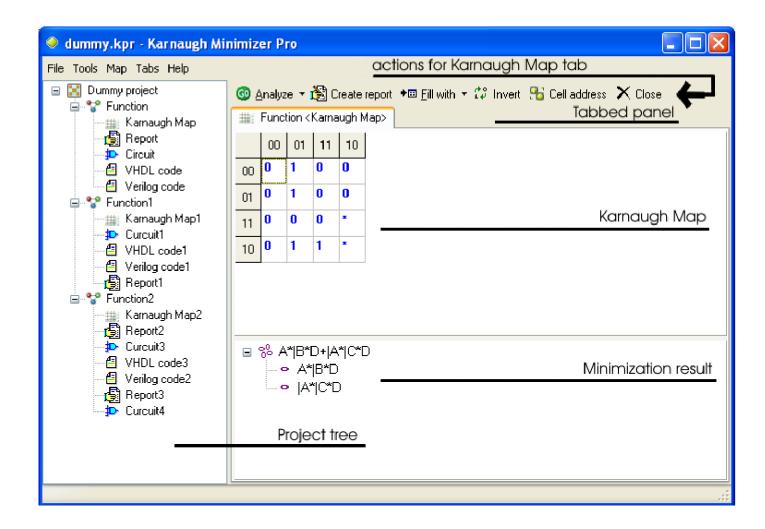

User interface of Karnaugh Minimizer Pro consist of two main parts:

- Project tree allow you to manage content of your project, you can add any number

of boolean functions to project tree using Ctrl-Alt-F shortcut or through main menu

"File | Add function". Each function node of project tree can contain unlimited number

of sub nodes with fixed types like Report, Circuit, VHDL code, Verilog code and only one

node of type Karnaugh Map.

- Tabbed panel allow you to browse through project tree nodes, Use F3 shortcut to add content of selected node to tabbed panel. Each tab has appropriate set of actions

Which can help you to operate with selected node content, for example Karnaugh Map tab has Analyze, Create report, Fill with, Invert, Cell address, Close actions.

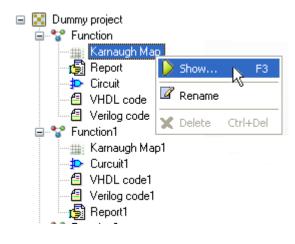

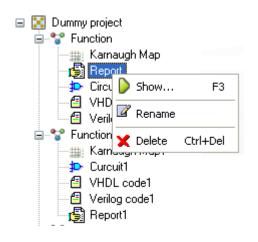

Right click on project tree brings up popup menu.

You can Show, Rename or Delete tree nodes.

**Show** - adds content of selected node to tabbed panel if it not already there, otherwise it will set corresponding tab as active.

Also you can do this by double clicking on tree node.

**Rename** - When you add nodes to tree, they will be named with default names, you can rename it for better understanding and quick search purposes.

**Delete** - allows you to remove unnecessary nodes from tree. Corresponding tab will be closed when you delete node with opened tab.

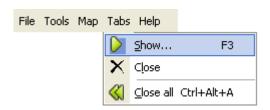

## **Using tabbed panel**

Tabbed panel - can simultaneously display as many tabs as you wish.

Use project tree popup menu to add content of selected node to tabbed panel. Each tab has "Close" action which allow you to close active tab. Also you can close all tabs if number of opened tabs too many.

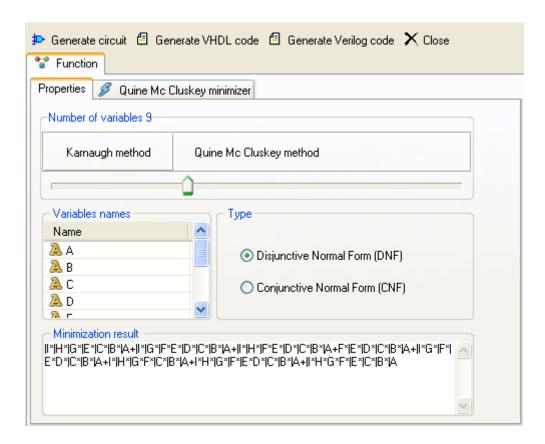

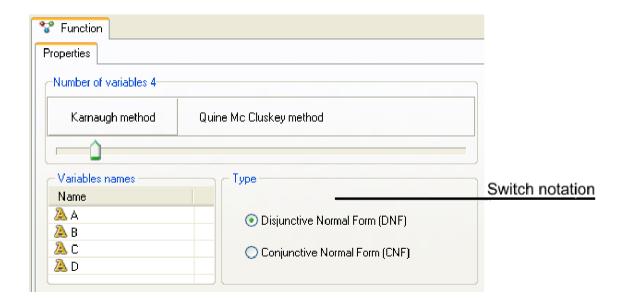

#### **Function tab**

Function tab represent properties of boolean function such as: variable count, variable names, type of function. This tab more important then others, because it define which minimization algorithm will be used for particular boolean function, it depends on how many Input variables used in function.

- Karnaugh map method is used when number of input variables between 2 and 8

- Quine Mc Cluskey method is used when number of input variables gain 9 and below 23

After minimization process, function tab will display "Minimization result" section, then you will be able to use actions for generating Circuit, VHDL or Verilog codes based on result of minimization.

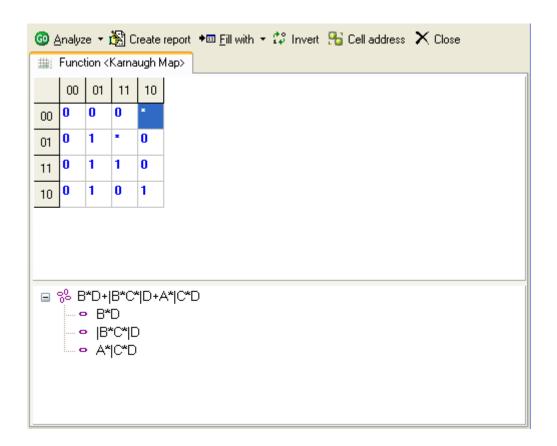

## Karnaugh Map tab

Karnaugh Map tab is used for minimization of boolean function by graphical method Karnaugh maps. This tab will help you to visualize minimization process and improve your understanding of this method of analyze.

Karnaugh map can be filled by several ways: with Truth table, Sets, Logic formula or with manual input of function values directly to map. Direct input can be done through keyboard or with mouse clicks.

After analyze of Karnaugh Map you will be able to use "Create report" action, which quickly and easily make detailed report of minimization process. Also you can open appropriate function tab and generate Circuit, VHDL or Verilog code.

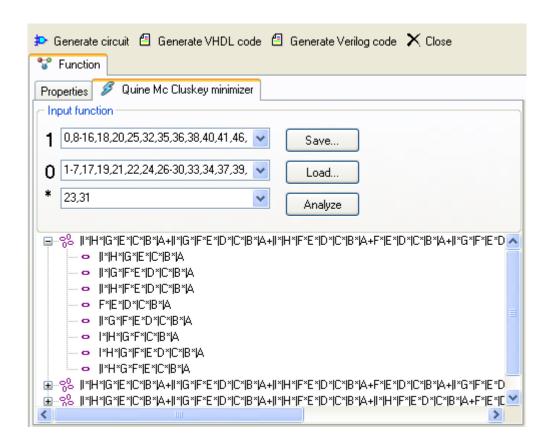

### **Quine Mc Cluskey tab**

This tab appears only when you move variables count slider to values more then 8. With Quine Mc Cluskey minimization algorithm you can handle boolean functions with number of Input variables from 9 to 23.

Boolean function can be defined with Sets representation only, because it is compactest way to store function. You will be able to Save, Load and Analyze boolean function. This tab will be accessible to registered users only.

After minimization process, function tab will display "Minimization result" section, then you will be able to use actions for generating Circuit, VHDL or Verilog codes based on result of minimization.

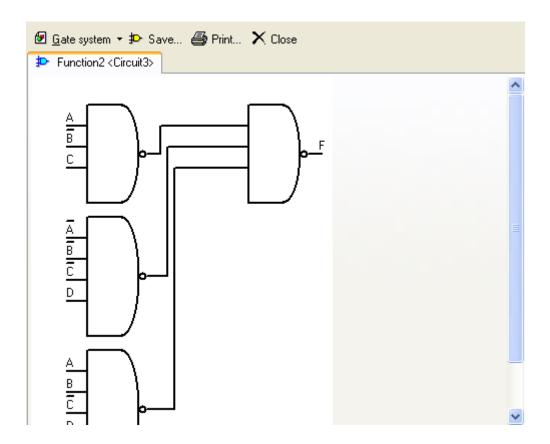

## **Circuit tab**

Circuit tab is designed for schematic drawing purposes only, it is possible to draw circuit with NAND gates and save it as JPG or BMP image. Also you can do switching between USA and European systems of gates .

You can generate circuit after minimization process from Function tab

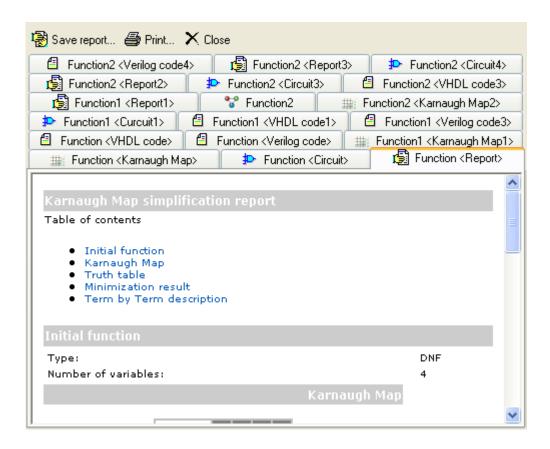

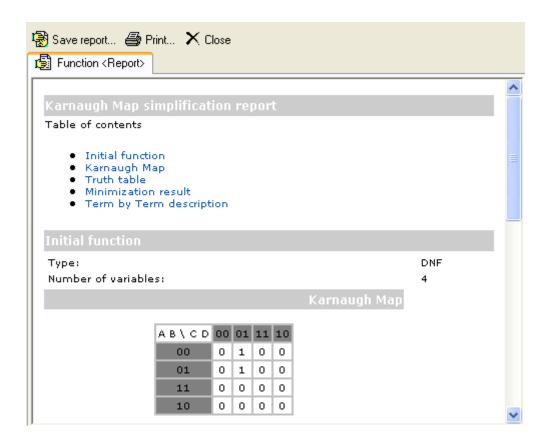

# Report tab

Report tab allow you to view, print and save reports of minimization process produced by Karnaugh Map tab

Report it is HTML document which you can easily edit with Word processor and add Circuit picture or VHDL or Verilog code.

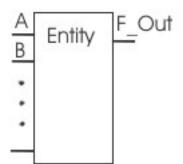

#### VHDL code tab

VHDL code tab is used to display generated by Function tab code.

VHDL is (Very high speed integrated circuit Hardware Description Language) code.

This codes created by Karnaugh Minimizer Pro can be used with any EDA Design/Verification tool include Active-HDL by Aldec inc.

VHDL code is used for verification and testing results of synthesis.

Created VHDL code has following structure:

Architecture for this entity is created with Simple Signal Assignment Statement (SSAS).

```

X Close

Function2 <VHDL code3>

library IEEE;

use IEEE.std logic 1164.all;

entity Boolean Function is

generic(delay : time := 1 ns);

port (

A: in std logic;

B: in std logic;

C: in std logic;

D: in std logic;

F Out : out std logic

);

end Boolean_Function;

architecture SSAS of Boolean Function is

signal z , k0, k1, k2 : std logic;

begin

k0 <= A and not B and C;

let are not a and not P and not C and D.

```

You can paste generated code directly to HDL design IDE without major changes in it structure.

# Verilog code tab

Verilog code tab is used to display generated by Function tab code.

Verilog (Verilog HDL - developed in 1984-1985 by Philip Moorby) code.

This codes created by Karnaugh Minimizer can be used with any EDA Design/Verification tool include Active-HDL by Aldec inc

Verilog code is used for verification and testing results of synthesis.

```

X Close

Function2 <Verilog code4>

module Boolean_Function (BF , A, B, C, D);

input A,B,C,D;

output BF;

// internal wires //

wire k0, k1, k2;

wire NotA, NotB, NotC, NotD;

// Not gates //

not (NotA, A);

not (NotB, B);

not (NotC, C);

not (NotD, D);

// And gates //

and (kO ,A, NotB,C);

and (k1 ,NotA, NotB, NotC,D);

and (k2 ,A,B, NotC,D);

// Or gates //

or (BF ,k0,k1,k2);

endmodule

```

You can paste generated code directly to HDL design IDE without major changes in it structure.

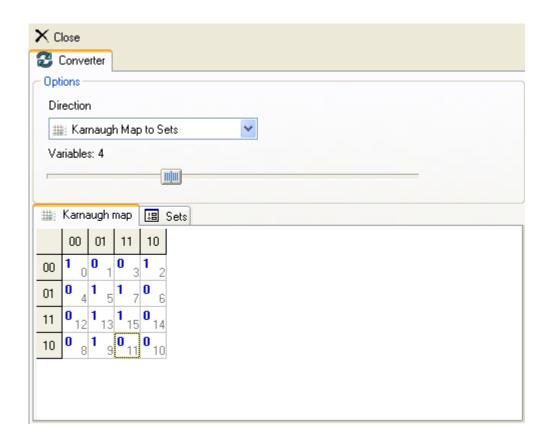

#### Converter tab

Converter tab is used for conversion purposes only not for minimization.

Converter tool allow you to convert Boolean function between different representations of it (Karnaugh map, Sets, Truth table) and it is limited to 8 variables because Karnaugh map method can handle maximum 8 variables.

First of all select direction of conversion, then adjust number of variables.

Next fill one of two parts and switch to another, you can do two way conversions with this tool.

#### **SOP and POS notations**

Boolean function can be represented in one of this two forms:

- SOP (Sum-of-Products) or DNF (Disjunctive Normal Form) focuses on the 1's in the output.

- POS (Product-of-Sums) or CNF (Conjunctive Normal Form) focuses on the 0's in the output.

In **SOP** The direct meaning variable corresponds logic "1" and inverse logic "0". In this form the terms united with "+"(Disjunction) and variable in a term united with "\*"(Conjunction).

**Example:** A\*B\*C + |A\*B\*|C + B\*C

In **POS** The direct meaning variable corresponds logic "0" and inverse logic "1". In this form terms united with "\*"(Conjunction) and variable in a term united with "+"(Disjunction).

**Example:** (A+B+C)\*(|A+B+|C)\*(B+C)

You can manage this notations on boolean function properties page.

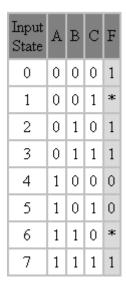

#### **Decimal notation**

Decimal notation is a short hand for specifying boolean functions. An example of decimal notation is:

SOP/DNF:

F = E(0,2,3,7), D(6,1).

POS/CNF:

F = A(4,5), D(6,1).

Note: D - Don't care

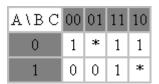

A function is specified either in SOP or POS. Sum(E) indicates SOP and Pi(A) indicates POS, D specifies don't care conditions (all don't care conditions are specified with sum). The best way to understand decimal notation is to show how to get it. We'll use the following system:

K-map for function F

| Α\ΒC | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 0    | 0  | 1  | 3  | 2  |

| 1    | 4  | 5  | 7  | 6  |

K-map for input states(Sets)

The inputs are A, B and C. The output is F. The key to decimal notation is a well defined arrangement of the inputs.

Each input is mapped to a bit in a binary number. In this case, C is bit 0, B is bit 1 and A is bit 2. The values of a particular input state are then represented by a binary number.

A=0, B=1, C=1 Input State = 011 (binary), 3 (decimal)

# What is RegKey?

**RegKey** - Registration Key is used to personalize copy of Karnaugh Minimizer similar with Serial Number (S/N) or Product code.

You can find your RegKey in main menu of Karnaugh Minimizer under "Help | About". RegKey have following structure: KMX-YYYYYYYYYYY where

X = S is Karnaugh Minimizer Standard edition.

X = P is Karnaugh Minimizer Professional edition.

YYYYYYYYYYYYYY - personal number for every copy of the program.

The RegKey is stored in Windows registry so if you ReInstall Windows you will lose your personal number and program will generate new one. If you are registered user simply mail new RegKey to support team of Karnaugh Minimizer and you will receive new license file.